# Single-phase DC Brushless Motor Driver IC

# ■ GENERAL DESCRIPTION

The NJU7327 is a single-phase DC brushless motor driver IC for small fan-motor and high power applications. It features MOS-FET driver circuit for better saturation characteristics. Slew late of amplifiers and feedback resistors are optimized to achieve low-noise motor operation. The NJU7327 also includes frequency generator (FG) output for various control needs.

# ■ FEATURES

- Operating Voltage  $V_{DD}$ =3.5 ~ 15V

- FG Output

- Internal Lock Detect

- Low Operating Current

- Low Saturation Output Voltage

Vsat=±0.35V @lo=±200mA

- C-MOS Technology

- VSP10 Package Outline

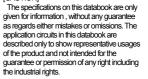

# ■ BLOCK DIAGLAM

# 1: LD 2: FG 3: V<sub>SS</sub> 4: OUT B 5: V<sub>DD</sub> 6: V<sub>DD</sub> 7: OUT A

■ PIN FUNCTION

8: V<sub>SS</sub> 9: IN-10: IN+

New Japan Radio Co., Ltd.

■ PACKAGE OUTLINE

| ■ABSOLUTE MAXIMUM RATINGS                       |                     |                                      |                    | (Ta=25°C) |                                 |      |       |  |

|-------------------------------------------------|---------------------|--------------------------------------|--------------------|-----------|---------------------------------|------|-------|--|

| PARAMETER                                       |                     | RATINGS SYMB                         |                    | OL (unit) |                                 | IOTE |       |  |

| Supply Voltage                                  |                     | +18 V                                |                    | /)        |                                 |      |       |  |

| Input Voltage                                   |                     | $-0.3 \sim V_{DD}$ +0.3              |                    | )         |                                 |      |       |  |

| Operating Temperature Range                     |                     | -40 ~ +85                            | Topr (°0           | C)        |                                 |      |       |  |

| Storage Temperature Range                       |                     | -50 ~ +150                           | Tstg (°0           | C)        |                                 |      |       |  |

| Power Dissipation                               |                     | 400                                  | P <sub>D</sub> (mV | V)        | Device itself                   |      |       |  |

| ■ RECOMMENDED OP<br>V <sub>DD</sub> =3.5V~15.0V |                     |                                      |                    |           |                                 |      | 0500) |  |

|                                                 |                     |                                      |                    |           | (V <sub>DD</sub> =12V, Ta=25°C) |      |       |  |

| PARAMETER                                       | SYSMBOL             | CONDITION                            |                    | 1IN.      | TYP.                            | MAX. | UNIT  |  |

| Operating Current                               | I <sub>DD</sub>     | No load                              |                    | -         | 3.0                             | 4.0  | mA    |  |

| Input Offset Voltage                            | V <sub>IO</sub>     | 1V bias                              |                    | -15       | -                               | 15   | mVp-p |  |

| Input Common Mode<br>Voltage Range              | V <sub>ICM</sub>    | -                                    |                    | 0.2       | -                               | 8.0  | V     |  |

| Maximum Output<br>Voltage Range                 |                     | lo=+200mA                            |                    | 1.55      | 11.70                           | -    |       |  |

|                                                 | V <sub>OM</sub>     | lo= -200mA                           |                    | -         | 0.30                            | 0.45 | V     |  |

| Slew Rate                                       | SR                  | RL=58.6Ω                             |                    | 46.2      | 60.0                            | 85.7 | mV/µS |  |

| Lock Detect Charge<br>Current                   | I <sub>CH</sub>     | -                                    |                    | 0.70      | 1.25                            | 2.25 | μA    |  |

| Lock Detect<br>Discharge Current                | I <sub>DIS</sub>    | -                                    |                    | 0.20      | 0.40                            | 0.80 | μA    |  |

| Clamp Voltage                                   | V <sub>CL</sub>     | -                                    |                    | 2.5       | 2.6                             | 2.7  | V     |  |

| Detect Voltage                                  | V <sub>LD</sub>     | -                                    |                    | ).54      | 0.60                            | 0.66 | V     |  |

| Thermal Shutdown<br>Temperature                 | T <sub>TSD</sub>    | -                                    |                    | -         | 180                             | -    | °C    |  |

| FG H Leak Current                               | I <sub>FGLEAK</sub> | IN+=12V, IN-=0V, $R_P$ =10k $\Omega$ |                    | -         | -                               | 1.0  | μA    |  |

| FG L Voltage                                    | V <sub>FGL</sub>    | IN+=0V, IN-=12V, $R_P$ =10k $\Omega$ |                    | -         | -                               | 0.3  | V     |  |

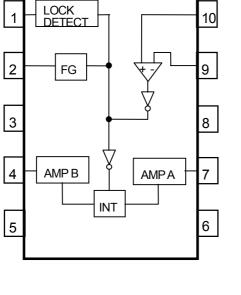

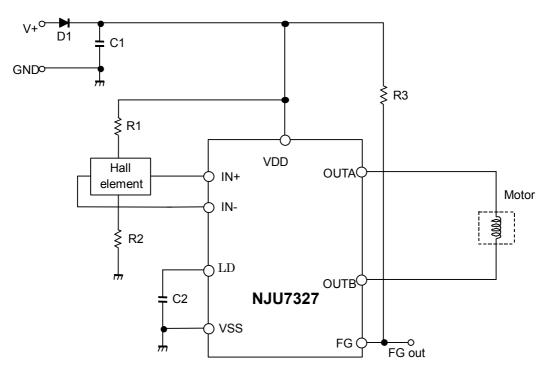

# ■ APPLICATION CIRCUIT

$\bullet$  Connect the decoupling capacitor between  $V_{\text{DD}}$  and  $V_{\text{SS}}.$

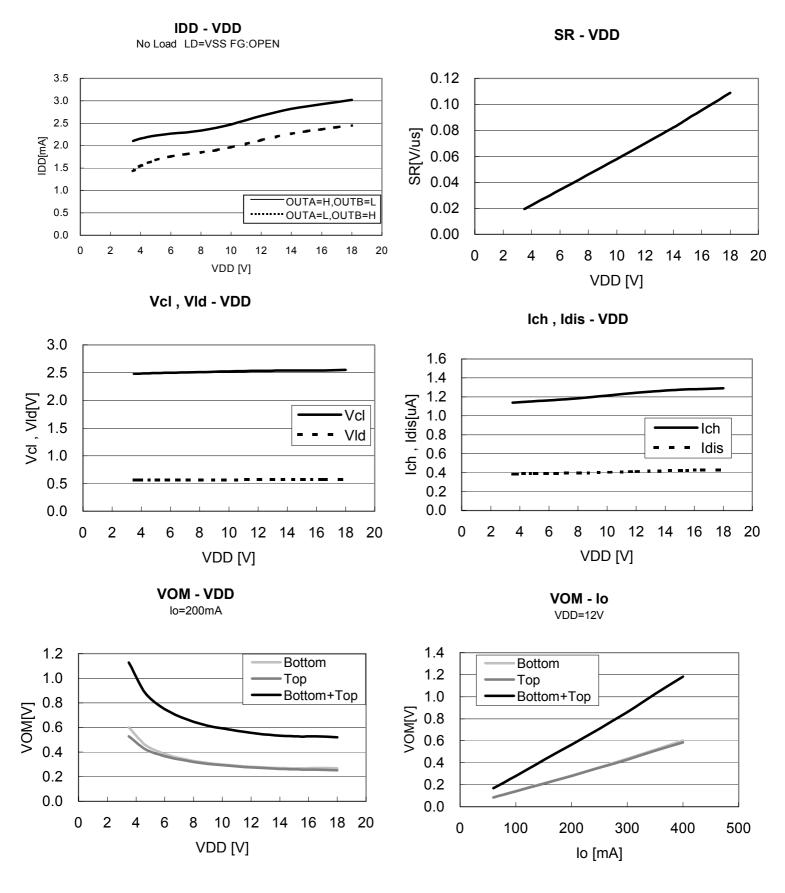

■ TYPICAL CHARACTERISTICS

New Japan Radio Co., Ltd.

# APPLICATION NOTE

The NJU7327 is a single-phase DC brushless motor driver IC in small VSP-10 package. With minimal external components, it can drive up to 200mA of motor current for small fan application.

# [Application Circuit Example]

# [Design Notes]

Above application example is designed for 12V operation with motor current of 200mA. It uses the following components:

Hall elements: HW101A (AKE)

1. Selection of C1 and D1:

C1 is used for a noise reduction purpose. A typical value is 0.1uF.

Optimize the value in actual operating conditions if necessary. D1 is a diode for protection against reverse voltage supply. Silicon rectifier diode (WO3C, 10D1 and equivalent) is appropriate.

2. Lock Protection Function (Design of C2 value):

Lock Protection Function, consists of Motor Lock Detection and Auto Resume Function, is a safety feature to protect a motor and a driver circuit from fatal destruction in case of motor halt.

Motor Lock Detection detects motor halt due to irregular load conditions and then cuts motor driving current f or safety operation. A value of C2 determines Lock detection time () and Auto Resume Time (Toff).

Lock detection time (Ton) is given by:

$$T_{ON} = C2 \frac{V_{CL} - V_{ID}}{Ich} [\text{sec}]$$

Where C2 is 0.47uF:

$$T_{ON} = 0.47 \times 10^{-6} \times \frac{2.6 - 0.6}{1.26 \times 10^{-6}} = 0.76 [\text{sec}]$$

Auto Resume Time (Toff) is given by:

$$T_{OFF} = C2 \frac{V_{CL} - V_{ID}}{I dis} [\text{sec}]$$

Where C2 is 0.47uF:

$$T_{OFF} = 0.47 \times 10^{-6} \times \frac{2.6 - 0.6}{0.42 \times 10^{-6}} = 2.33 [\text{sec}]$$

In actual application, Lock detection time (Ton) is affected by the mechanical time constant of a motor. Therefore, constant start up must be confirmed in actual evaluation taking operating variations (i.e. Temperature, Voltage change and so on) in consideration.

A typical value of C2 is either 0.47uF or 1uF depending on a motor.

# 3. Design of hall element bias resistance (R1 and R2)

Hall amplifier is a differential amplifier.

The common-mode input voltage is between 0.4V and VDD-1V and the input signal must be within the range. Non-excitation hall bias voltage is to be set at a half of VDD for effective use of common-mode input voltage range. Therefore the same value of hall bias resistors is selected for R1 and R2. Given that the bias current is set to be 5mA by HW101A datasheet, R1 and R2 can be determined as follows:

$$R1 + R2 + Rin = \frac{VDD}{Ihbias} = \frac{12}{5 \times 10^{-3}} = 2.4k\Omega$$

$$R1 = R2 = 1k\Omega$$

The output voltage of hall elements is influenced by the bias current and magnetic flux density of hall elements. The optimum input voltage of NJU7327 is 100mVp-p and higher. With such input voltage, the highest efficiency can be obtained.

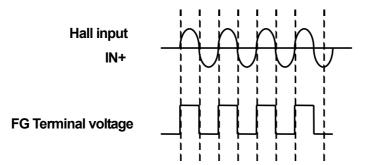

4. Design of FG output resistance (R3)

FG Out (FG: Pin8) is an open drain output and R3 is a pull up register. A typical value of R3 is  $10k\Omega$ . The timing chart of FG Out is as follows.

Note that the pull up resistance shall be connected to below supply voltage.